Hello, this is Tanizawa, a first-year master’s student.

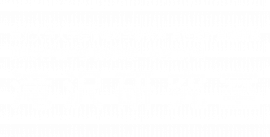

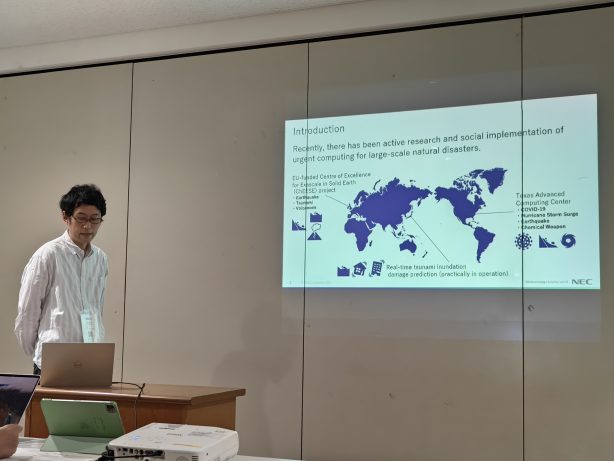

On December 12–13, 2024, Professor Takizawa from our laboratory gave a lecture at the 38th Workshop on Sustained Simulation Performance (WSSP38).

WSSP is a workshop jointly organized by Tohoku University’s Cyber Science Center and the High-Performance Computing Center Stuttgart (HLRS) in Germany. This time, both presenters and attendees participated in person at the Cyber Science Center, and the event saw a large turnout, making it a great success.

For details on the workshop program, please refer to this link.

Each presentation was highly insightful, and the workshop reinforced my motivation to contribute to the HPC field.