2/28に分野横断セミナーが,2/29にテクノフェスティバル/マッチメイキングセッションが開催されました.

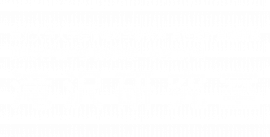

残念ながら,今年度は新型コロナウイルスの影響もあり,ほぼポスターを展示するだけとなりました.

分野横断セミナーはM1学生が1年間の研究成果とこれから1年の研究方針をまとめて他分野の学生に発表する,1年のけじめとなるイベントです.

当研究室からは,渡辺くん,劉くん,柯くん,江端くんが発表を行いました.

2/29(土)に本学サイエンスキャンパスホールにて発表を行う劉さん

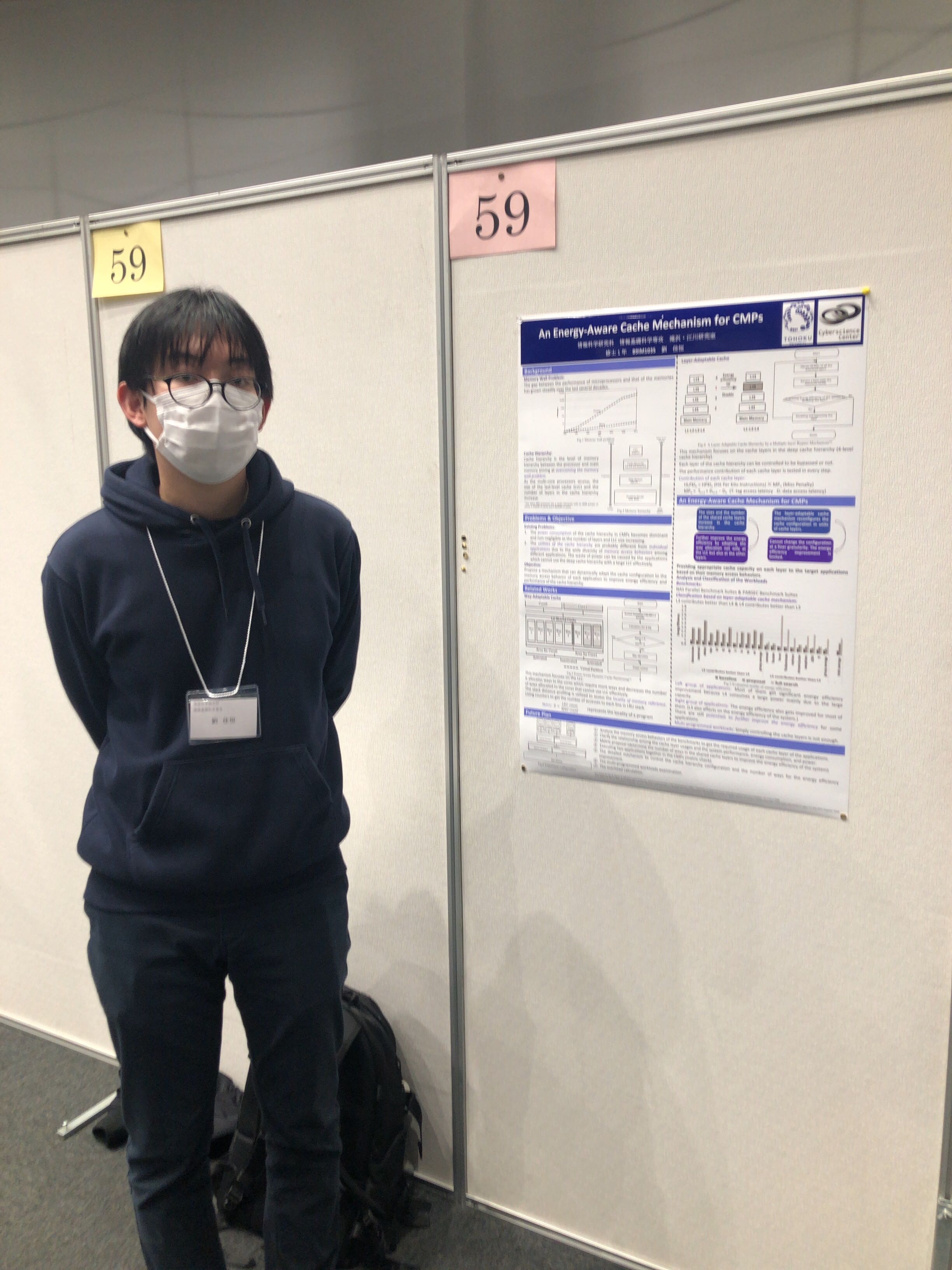

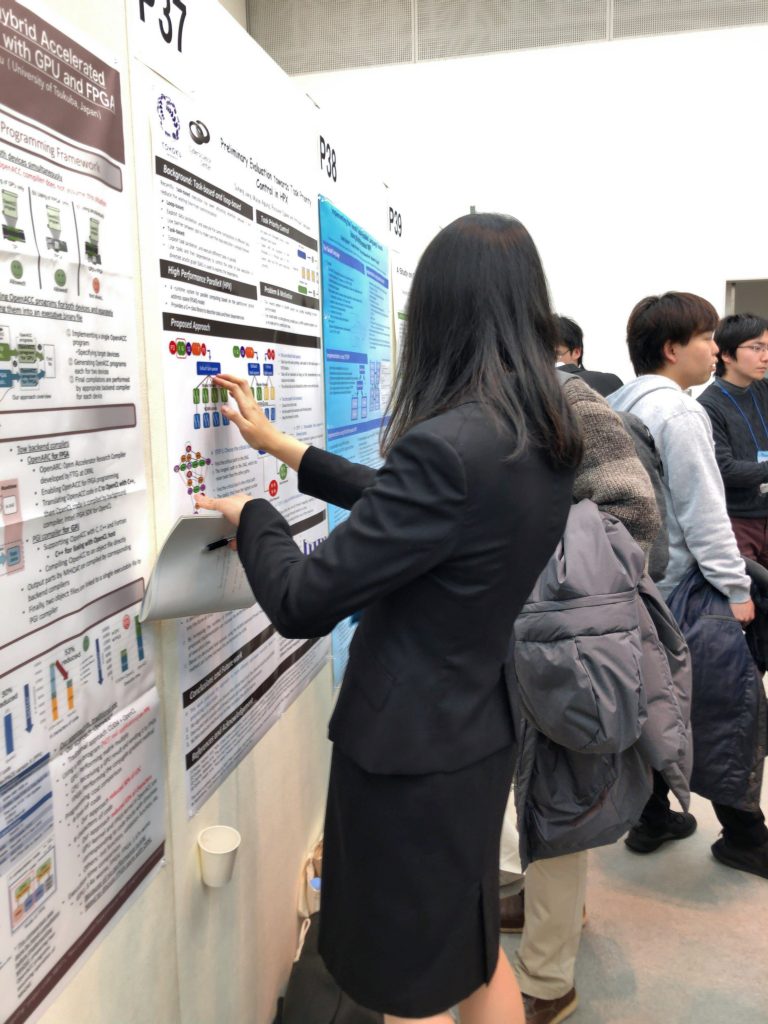

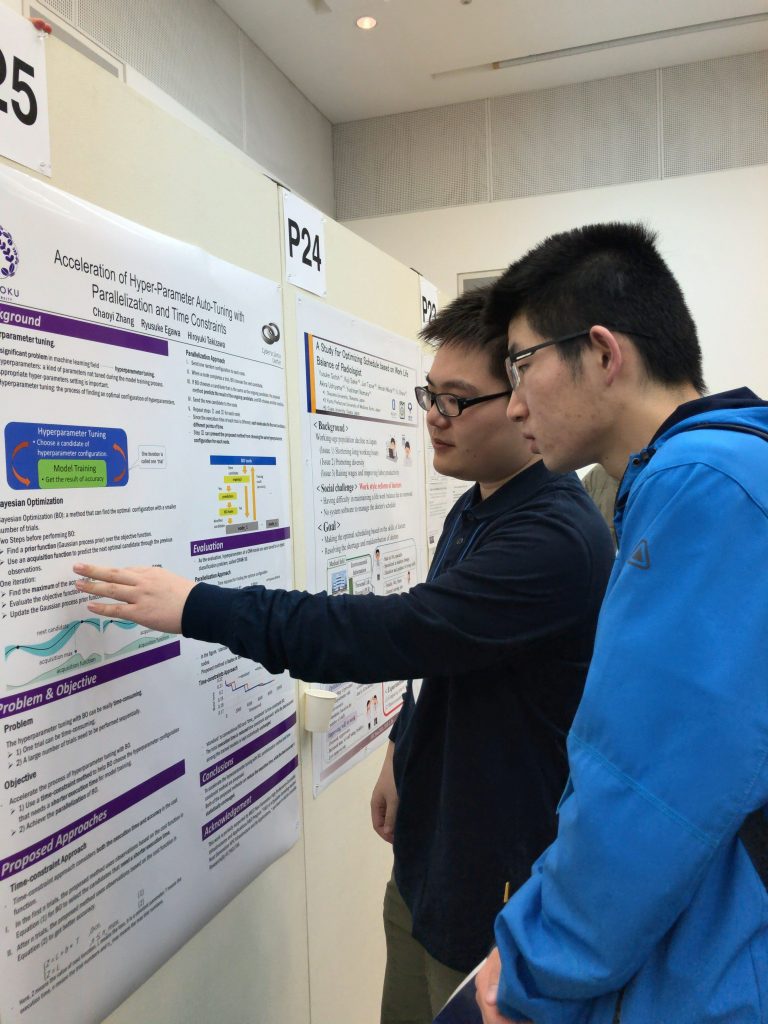

HPC Asia 2020においてJiangさん、Zhangさんがポスター発表

1/15~17にかけて福岡市でHPC Asia 2020が開催されました。

本研究室からは、M2のJiangさんとZhangさんが参加し、ポスター発表を行ってきました。

Preliminary Evaluation towards Task Priority Control in HPX

Preliminary Evaluation towards Task Priority Control in HPX

Suhang Jiang (Tohoku Univ.), Mulya Agung (Tohoku Univ.), Ryusuke Egawa (Tohoku Univ.), Hiroyuki Takizawa (Tohoku Univ.)

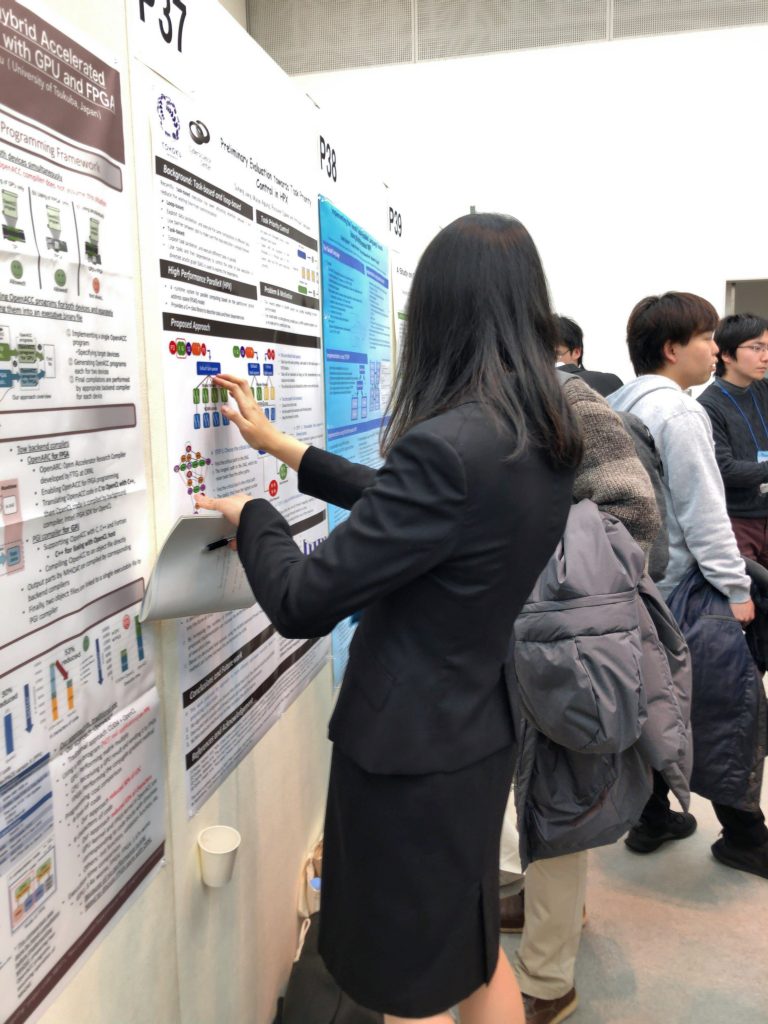

Acceleration of Hyper-Parameter Auto-Tuning with Parallelization and Time Constraints

Acceleration of Hyper-Parameter Auto-Tuning with Parallelization and Time Constraints

Chaoyi Zhang (Tohoku Univ.), Ryusuke Egawa (Tohoku Univ.), Hiroyuki Takizawa (Tohoku Univ.)

発表内容の詳細はこちらから:

http://sighpc.ipsj.or.jp/HPCAsia2020/program.html

Poster Presentation at HPC Asia 2020

HPC Asia 2020 was held in Fukuoka City from 15th to 17th Jan.

Two M2 students participated and presented their posters.

Preliminary Evaluation towards Task Priority Control in HPX

Preliminary Evaluation towards Task Priority Control in HPX

Suhang Jiang (Tohoku Univ.), Mulya Agung (Tohoku Univ.), Ryusuke Egawa (Tohoku Univ.), Hiroyuki Takizawa (Tohoku Univ.)

Acceleration of Hyper-Parameter Auto-Tuning with Parallelization and Time Constraints

Acceleration of Hyper-Parameter Auto-Tuning with Parallelization and Time Constraints

Chaoyi Zhang (Tohoku Univ.), Ryusuke Egawa (Tohoku Univ.), Hiroyuki Takizawa (Tohoku Univ.)

Please check the details at the following website:

http://sighpc.ipsj.or.jp/HPCAsia2020/program.html

New Year Party

Happy New Year!

The new year party was held on 25th Jan with Kobayashi Sato Lab.

Peace gesture from prf. Egawa✌

Peace gesture from prf. Egawa✌

Closing address from prof. Takizawa

Closing address from prof. Takizawa

一本締め(hand-clapping performed to celebrate the conclusion or completion of something in Japanese culture)

一本締め(hand-clapping performed to celebrate the conclusion or completion of something in Japanese culture)

A lot of people came to this party.

A lot of people came to this party.

Wishing for a year filled with laughter, success, and peace my dear labmates.

研究室合同新年会の開催

明けましておめでとうございます。

1月9日に小林・佐藤研と合同で新年会が開催されました。

江川先生からのピース✌

江川先生からのピース✌

滝沢先生の締めの挨拶

滝沢先生の締めの挨拶

一本締め

一本締め

大勢の方々に参加していただきました

大勢の方々に参加していただきました

本年もどうぞ、よろしくお願い申し上げます。

Year-end party

The year-end party was held today.

Both professors and students shared pizza, chicken, and hand-made cup-cakes.

Merry Chrismas and Happy New Year.

忘年会兼クリスマスパーティーが開催されました

研究室のメンバーでピザを囲みながら忘年会を行いました。

Imoni Party was Held

On 27th Oct, the yearly imoni party was held with Kobayashi Lab. together. This year, in total, around 40 students attended, as well as professors with their families.

4th-year-undergraduate students were the leading members to prepare this party, from burning the fire to cooking. A lot of foods, including imoni-pot and yakitori were made.

All students and professors had a great chance of chatting with each other.

芋煮会が開催されました

滝沢・江川研と小林・佐藤研合同の芋煮会が10月27日に開催されました.

山形,宮城風芋煮のほか,おでんやちゃんこ鍋など沢山の鍋を囲みながら,皆で楽しい時間を過ごしました.

滝沢教授,江川准教授が30th WSSPで発表を行いました.

滝沢教授,江川准教授が10月9日,10日にドイツシュトゥットガルト大学高性能計算センター(HLRS)で開催された30th Workshop on Sustained Simulationで発表を行いました.

OpenCL-like Offload Programming on SX-Aurora TSUBASA

Hiroyuki Takizawa

Heatstroke Risk Managements with High-performance Computing

Ryusuke Egawa