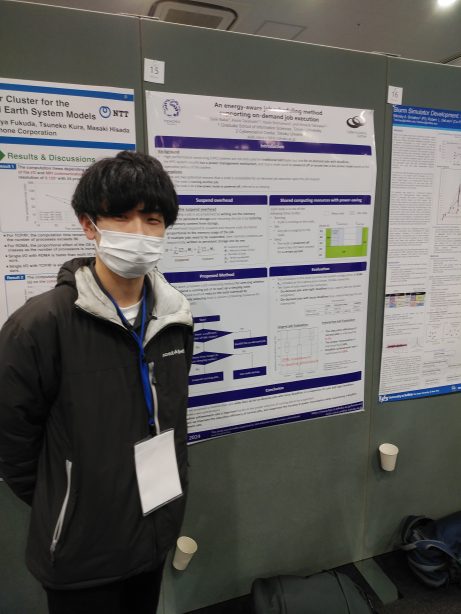

Hello, this is Tanizawa from B4.

graduation research presentation program was held on February 13~14. With the help of my professors and seniors, I was able to successfully complete my presentation.

I was able to listen to the research of other students in the aerospace engineering course at the presentation, which was very interesting and informative.

Now we will start writing our graduation theses. I will keep working hard until the deadline on March 4!