Hello there, long time no see. This is mellow.

Just around 1 hour before writing this article, we had the this year’s final, 8th, study session for B3 students.

What are B3 study sessions

As we’ve already explained in the page For Prospective Students, Takizawa lab prepares various educational programs for students who are new to the lab.

This year, we welcomed three B3 and one M1 freshmen to our lab. Thus, we had the study sessions for these four freshmen.

This year’s study session

In total, 8 study sessions were held this year with different and useful themes.

| Date | Tutor | Content |

|---|---|---|

| 17th June | Kaneko | Environment Construction |

| 24th June | Kaneko | Git & GitHub |

| 1st July | Matsuse | LaTeX |

| 8th July | Sugawara | C |

| 9th July | Sasaki | Parallelization |

| 15th July | Furuhata | Singularity |

| 29th July | Satake | Python |

| 5th Aug | Minglu | Machine Learning |

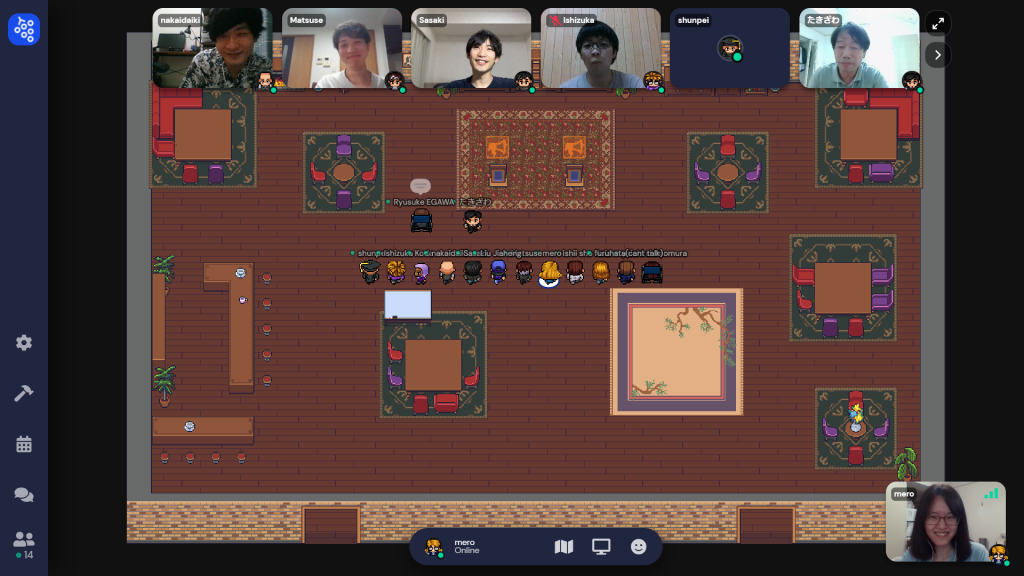

Each study sessions were like the following photo.

Hope what students have learned in these sessions can help with their further research activities in our lab.

That’s all here. Enjoy your summer vacation~